|

Автоматическое тестовое оборудование с подвижными пробниками в производстве электронных изделий (продолжение)

Прототипная и пилотная электронная продукция (электронные модули) малой и средней серийности, в том числе аэрокосмического и оборонного назначения, должна быть на 100% надежна при самых экстремальных по температуре, давлению и вибрациям условиях эксплуатации. Для электрического тестирования такой продукции в условиях производства оптимальным образом подходят безадаптерные универсальные тестеры с подвижными пробниками типа S40 Pilot. Универсальность, отсутствие необходимости изготовления тестовых адаптеров и разработка программы тестирования методом трансляции данных из систем САПР значительно сокращают время подготовки производства и делают это решение идеальным и единственно возможным при производстве спецтехники, так как обычно такое производство имеет мелкосерийный и многономенклатурный характер.

Программирование тестера S40 PILOT

Электронные компоненты бортового процессора современного самолета монтируются на обеих сторонах многослойной печатной платы размером 250x170 мм. Данный модуль имеет порядка 700 электрических цепей, к которым подключено примерно 200 компонентов, включая 80 интегральных микросхем, 70 емкостей и т.д. При наличии файла САПР тест на КЗ/обрывы для тестера с подвижными пробниками S40 Pilot создается и отлаживается за 30-40 минут. Время создания полной тестовой программы анализа производственных дефектов (MDA) - примерно 10-12 часов. Типовое время тестирования такого сложного изделия составляет 10-15 минут. Заметим, что ручная прозвонка на КЗ/обрывы электрических цепей такого или аналогичного по сложности модуля, которая, как правило, и используется в реальных условиях производства спецтехники, требует не менее 3-4 дней. Хорошо известно, что сопутствующий такой операции человеческий фактор не позволяет на 100% обеспечить требуемую высочайшую надежность изделия.

Рис. 1. Порядок создания тестовой программы для тестера S40 Pilot

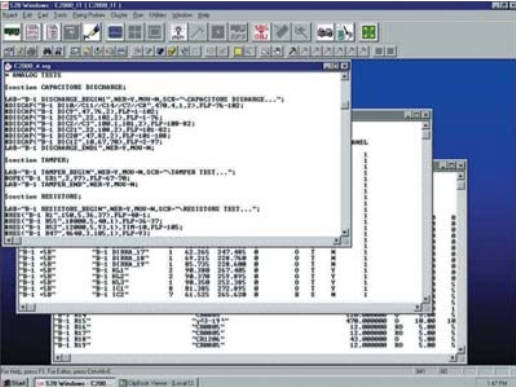

Разработка программы тестирования для тестера с подвижными пробниками реализуется автоматически методом трансляции из систем САПР. Отметим, что на данный момент тестером поддерживается 39 систем САПР, включая такие популярные в России, как PCAD (любые версии), ORCAD, Protel, Mentor и т. д. Программное обеспечение тестера - S20 Win функционирует под управлением операционной системы Windows 2000. Управляющая программа S20 Win и фрагмент тестовой программы для изделия пользователя представлены на рис.2.

Рис. 2. Тестовая программа системы S40 Pilot

При отсутствии файлов САПР тестовые программы могут создаваться вручную. При этом координаты тестовых точек вводятся в программу последовательно с помощью имеющейся в тестере видеокамеры. Кроме того, в качестве альтернативного метода создания тестовых программ может применяться опция автоматического обучения (autolearn), которая позволяет создавать тестовые программы при наличии заведомо годного эталонного изделия за несколько часов.

Из рис.1 ясно, что на выходе транслятора, входящего в состав управляющей программы S20 Win появляется основной модуль тестовой программы (файл с расширением File.srg).

Ниже дается пример рекомендуемой последовательности составления программы тестирования. Как правило, программа подразделяется на четыре блока.

- Разряд конденсаторов с последующим тестом на обрывы/КЗ.

- Аналоговый внутрисхемный тест (включая безвекторное тестирование), выполняемый без подачи на проверяемый электронный модуль напряжения питания.

- Цифровое внутрисхемное тестирование и (при необходимости) частичное функциональное тестирование, выполняемые с подачей на проверяемый электронный модуль напряжения.

- Заключительная секция программы для комментариев.

Хочется рассеять довольно распространенное среди специалистов мнение о повышенной сложности программирования тестера S40 Pilot. Реальный опыт эксплуатации системы показывает, что для работы на тестере в качестве оператора достаточно специалиста со средним техническим образованием, прошедшего курс специального обучения, а с программированием справится инженер-схемотехник. Илишь в тех случаях, когда тестер используется и для функционального тестирования сложных электронных блоков, к работе, связанной с созданием тестовых программ, в качестве консультантов привлекают конструкторов-разработчиков. Подчеркнем, что среднее время, затрачиваемое на создание тестовой программы для типового электронного модуля (150 электрических цепей и примерно такое же количество компонентов) составляет 10-12 часов. Понятно, что затраты времени во многом зависят от квалификации специалиста.

Внутрисхемное аналоговое тестирование

Очень часто в специализированной литературе под термином внутрисхемного аналогового тестирования понимается анализ производственных дефектов (MDA - Manufacturing Defects Analysis). При реализации данного тестирования системой S40 Pilot контролируются: номиналы резисторов, конденсаторов и индуктивностей, производится полноценная проверка полупроводниковых компонентов (диодов, стабилитронов, транзисторов), проверка трансформаторов и реле, а также выполнение многопроводных измерений. В качестве примера внутрисхемного аналогового тестирования рассмотрим то, каким образом системой S40 Pilot реализуется измерение сопротивления.

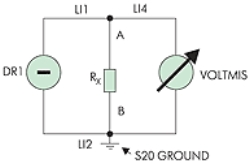

Измерение резистора производится путем пропускания электрического тока такой величины, которая необходима для вызова фиксированного падения напряжения (обычно 0,3 В). Другой контакт резистора на время проведения измерения подключается к общей точке измерительной системы тестера.

Рис. 3. Измерение сопротивления резистора

Для проведения этого теста необходимо установить следующие соединения между резистором и приборами и линиями измерительной платы LAM:

- DR1 (генератор тока) на линии LINE 1 (LI1) к точке A;

- S20 GROUND (общий провод) на линии LINE 2 (LI2) к точке B;

- VOLTMIS (вольтметр) подключенный на линии LINE 4 (LI4) к точке A.

Измерение производится путем пропускания электрического тока по линии LINE 1, величина которого была предварительно вычислена по формуле:

I = V/RX I = 0,3/RX

с последующим измерением величины падения напряжения на резисторе по показаниям вольтметра VOLTMIS, коммутируемого по линии LINE 4.

Рис. 4. Аппаратная реаоизация инмерения характеристик резистора

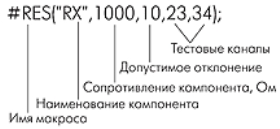

Все операции, необходимые для проведения измерения, то есть вычисление характеристик тока, подключение приборов и линий к измеряемому резистору, включены в макрос пользователя #RES.

Предположим, что резистор RX имеет номинальное сопротивление 1 кОм, допустимое отклонение составляет 5%, и для измерения будут использованы виртуальные тестовые каналы 23 и 24. Макрос пользователя примет такой вид:

Рис. 5. Макрос #RES для измерения характеристик резистора

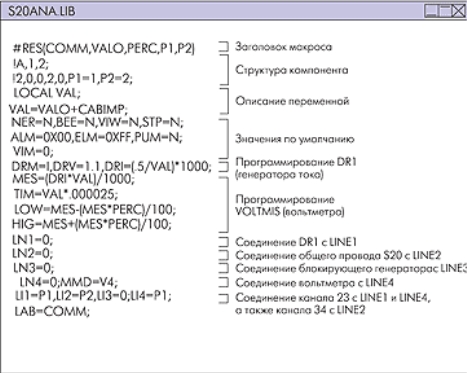

Данный макрос во время создания программы автоматически заносится в File.srg (основной программный модуль), который содержит информацию, необходимую для тестирования всех компонентов проверяемой платы, а соответствие макроса #RES и программных команд, которые управляют приборами и линиями, содержится в File.lib (файле библиотеки). На рис. 6 представлен фрагмент файла библиотеки S20ANA.LIB с описанием макроса пользователя #RES.

Рис. 6. Фрагмент файла библиотеки S20ANA для макроса #RES

Заметим, что наряду с основным макросом #RES для измерения резисторов (в зависимости от особенностей электрической схемы) могут быть использованы следующие макросы:

- #RESV - измерение резистора с напряжением определяемым пользователем;

- #RESHV - измерение резистора высоким напряжением;

- #RES4 - измерение резистора с помощью 4-проводных измерений;

- #RESХ - измерение резистивной матрицы;

- #RESCON - измерение резистора зашунтированного неполярным конденсатором;

- #RESCONV - измерение резистора зашунтированного неполярным конденсатором с напряжением определяемым пользователем;

- #RESCAP - измерение резистора зашунтированного полярным конденсатором;

- #RESCAPV - измерение резистора зашунтированного полярным конденсатором с напряжением определяемым пользователем;

- #TRIM - измерение подстроечного резистора.

Методика аналогового ограждения (Analog Guarding)

В связи с тем, что при выполнении внутрисхемного тестирования мы постоянно имеем дело с измерением компонентов впаянных в реальные электрические цепи, которые шунтируют и вносят искажения в процесс измерения, совершенно очевидно то, что мы должны иметь возможность компенсации такого рода ошибок. Для их устранения существует специальная технология, называемая аналоговым ограждением или аналоговым блокированием.

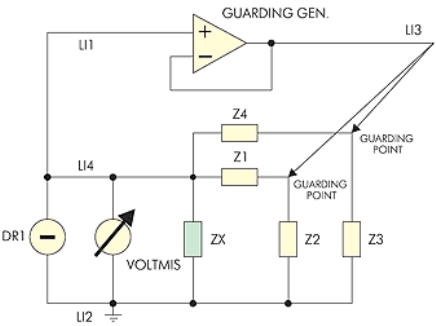

Рис. 7. Применение аналогового ограждения при измерении резистора

Методика ограждения используется для изолирования или вычленения отдельного компонента от остальной части электронной схемы при его тестировании. Для этого применяется метод выравнивания напряжений, которые присутствуют вокруг испытываемого компонента, с тем, чтобы в сопряженных с испытуемым компонентах отсутствовал электрический ток. Такая операция становится возможной благодаря наличию в тестере S40 Pilot специализированного ограничивающего генератора (GUA), состоящего из повторителя напряжения, поступающего с DR1, которое будет подаваться ко всем компонентам, соединенным с тестируемым узлом схемы. Таким образом, приложенный ток будет полностью проходить через испытываемый компонент и при этом будут исключены утечки тока в смежных узлах (точках ограждения). На рис. 7 представлен пример применения метода аналогового ограждения при тестировании.

Из представленного рисунка понятно, что разность потенциалов на компонентах Z1 и Z4 равна нулю, поэтому через них не проходит электрический ток. Весь электрический ток проходит через тестируемый компонент (ZX).

Безвекторное тестирование

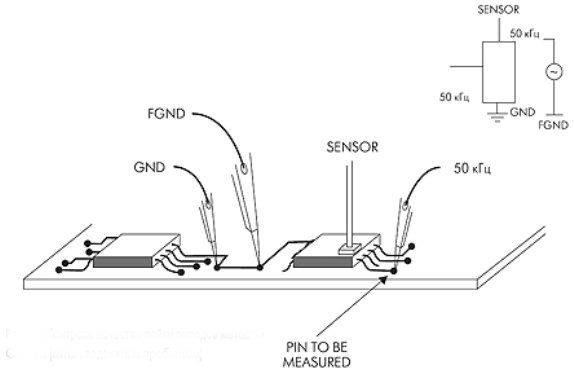

Наличие в тестере S40 Pilot опции безвекторного тестирования (vectorless test) значительно повышает тестовое покрытие проверяемого изделия. Главной задачей такого тестирования является проверка наличия и корректность припайки того или иного электронного компонента на тестируемом изделии. Для того чтобы воспользоваться всеми преимуществами данного метода, тестер необходимо программировать в автоматическом режиме. Другими словами, программирование тестера осуществляется автоматически, на основе данных САПР тестируемого изделия. Например, для программирования теста качества пайки микросхемы емкостным методом (OpenFix) в программу тестера из файлов САПР транслируются координаты корпуса и расположения контактных выводов проверяемой ИМС. Согласно этой информации осуществляется безвекторный контроль, заключающийся в позиционировании на корпус ИМС емкостного пробника с последующим измерением сигналов переменного тока, поступающих на него через входы-выходы проверяемой ИМС с подвижных пробников тестера. При отсутствии качественного контакта (непропай) между выводом микросхемы и ее контактной площадкой измеренное напряжение (RMS) будет на 50% меньше ожидаемого.

Рис. 8. Контроль качества пайки выводов ИМС методом Openfix

Рис. 9. Контроль качества пайки выводов ИМС методом Openfix (пятым подвижным пробником)

Цифровое внутрисхемное тестирование

Цифровое внутрисхемное тестирование системы S40 Pilot позволяет дополнительно повышать тестовое покрытие проверяемого изделия путем верификации прохождения критических сигналов через контрольные точки проверяемой электрической схемы. Следует четко понимать, что цифровое тестирование системы S40 Pilot имеет определенные ограничения, связанные с небольшим количеством подвижных пробников тестера (всего 4). Однако его эффективность может быть значительно повышена внесением в тест дополнительных подпружиненных пробников на магнитных подставках. Кроме того, тестер S40 Pilot позволяет дополнительно использовать в тестовой программе до 1024 каналов, коммутируемых с проверяемым устройством при помощи краевого разъема или специальных клипс. К преимуществам реализации цифрового внутрисхемного тестирования на тестерах с подвижными пробниками по сравнению с адаптерными системами следует отнести:

- низкие затраты на инжиниринг процесса тестирования (отсутствие необходимости в стационарных адаптерных устройствах);

- ускоренное время создания тестовых программ.

Рис. 10. Дополнительные пробники на магнитных подставках

Разумная стратегия тестирования цифровой части проверяемого электронного модуля заключается в запитывании изделия с последующим поблочным контролем его функционирования. Другими словами, наличие корректных сигналов в контрольных точках проверяемого электронного модуля позволяет судить о его общей работоспособности перед заключительным функциональным тестированием, выполняемым после монтажа данного модуля в готовое электронное устройство.

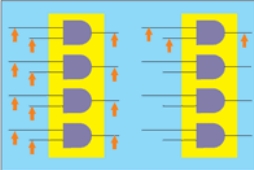

В качестве альтернативы может быть предложена тестовая стратегия с использованием безвекторного контроля для всей ИМС или блока проверяемого электронного модуля с последующим цифровым векторным тестированием одной их части (рис. 5).

Рис. 11. Технология уменьшения пробников на многовентильной интегральной микросхеме. Подразумевается, что КЗ и обрывы (левая часть рисунка) проверяются безвекторными методами тестирования

Методика цифрового ограждения (Digital Guarding)

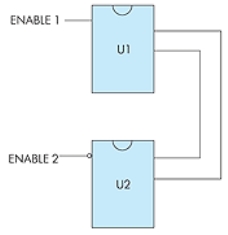

Как правило, цифровая схемотехника имеет шинную архитектуру, что подразумевает параллельное подключение большого количества интегральных микросхем к общим шинам устройства. При проведении цифрового тестирования на проверяемую плату должно быть подано электропитание, достаточное для того, чтобы цифровые компоненты начали взаимодействовать между собой. При использовании методики цифрового ограждения система тестирования может испытывать каждый цифровой компонент отдельно, путем отключения подключенных к нему посредством общей шины других цифровых компонентов. Данный принцип наглядно демонстрируется следующим примером:

При цифровом ограждении компонент U2 отключается путем подачи сигнала высокого уровня на контакт ENABLE 2, в это время тестируется компонент U1. При тестировании компонента U2 производится принудительное блокирование компонента U1 подачей сигнала низкого уровня на контакт ENABLE 1. Таким образом, может быть реализовано отдельное тестирование для каждого из данных компонентов.

Рис. 12. Принцип цифрового ограждения

Продолжение следует.

Игорь Марков,

Игорь Рыков

|