|

Владимир Мистюков, Павел Володин, Владимир Капитанов

Окончание, начало в № 4, 2000

Однокристальная реализация алгоритма БПФ на ПЛИС фирмы Xilinx

Дальнейшее повышение производительности однокристальной обработки

В общем случае при построении М-модуля БПФ можно пойти несколькими путями: либо спроектировать модули с малыми занимаемыми объемами, большим временем преобразования и малой скоростью поступления входных данных (до 15 МГц), либо реализовать скользящий БПФ с малым временем преобразования и большой скоростью поступления данных (до 150 МГц). Второй путь, хотя и позволяет получить великолепные результаты по быстродействию, но характеризуется значительными аппаратными затратами, зачастую распределяющимися на несколько кристаллов. Однако в последнее время в связи с появлением ПЛИС фирмы Xilinx большого объема (до 4 млн логических вентилей) и с больших числом внешних пользовательских выводов стала возможным однокристальная реализация высокоскоростного скользящего преобразования Фурье с непрерывным поступлением данных на частотах до 150 МГц. Основная идея реализации скользящего БПФ состоит в том, что для вычислений на каждой ступени используется отдельный законченный блок, обеспечивается конвейеризация в пределах не только одной ступени, но и всего модуля. При этом время преобразования будет равным времени вычислений на одной ступени. Структура блока обработки приведена на рис. 7.

В табл. 4 представлены ориентировочные данные по быстродействию и занимаемому объему М-модулей БПФ, построенных в соответствии с данным алгоритмом.

Рис. 7. Структура однокристального скользящего БПФ на ПЛИС Virtex

Маршрут проектирования и аппаратная реализация БПФ на ПЛИС

Маршрут проектирования устройства ЦОС на ПЛИС Xilinx с использованием специализированных библиотек М-модулей, в том числе БПФ, представлен на рис. 8 [7].

Рис. 8. Маршрут проектирования устройства ЦОС на ПЛИС Xilinx

Ввод проекта возможно осуществлять несколькими способами:

- интерактивный графический ввод в схемотехническом редакторе;

- текстовый ввод на языке описания аппаратуры высокого уровня;

- диаграммами состояний конечного автомата.

При вводе проекта используются библиотеки стандартных логических функций и дополнительные макробиблиотеки (БПФ, цифровые фильтры, PCI, VME и т. п.).

Затем выполняется моделирование проекта с верификацией заданных функций и топологическая трассировка ПЛИС.

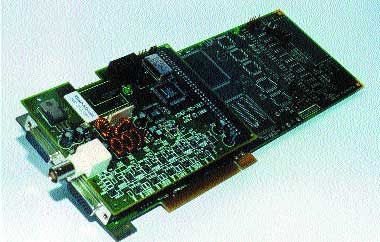

Аппаратная реализация описанных М-модулей БПФ выполнялась с использованием отечественных инструментальных модулей XDSP-680 и SETCORE-1M [8, 9]. Что представляют собой данные модули? В основе XDSP-680 лежит плата с разъемом PCI 33/32, содержащая до 4-х ПЛИС Xilinx серий Spartan/XC4000 с общим объемом до 680 тыс. вентилей, восемь банков высокоскоростного ОЗУ 128 КЅ8 и два банка flash-памяти (рис. 9). Модуль SETCORE-1M предусматривает установку одной ПЛИС серии Virtex с объемом до 800 тыс. вентилей, шести банков статического ОЗУ 64 КЅ16, flash-памяти до 16 Мбит (рис. 10).

Рис. 9. Внешний вид инструментального модуля XDSP-680

Оба инструментальных модуля содержат внешние цифровые порты и предусматривают установку дочерних плат, например АЦП/ ЦАП, процессор ЦОС, дополнительное ОЗУ, оптический интерфейс. Таким образом, меняя конфигурацию устанавливаемых дочерних плат под определенную задачу, модули позволяют за счет универсальности решать практически любые задачи цифровой обработки сигналов — от цифровой фильтрации, в том числе двумерной, до спектрального анализа и многоканальной корреляционной обработки.

Рис. 10. Внешний вид инструментального модуля SETCORE-1M

М-модуль БПФ на серии Spartan был применен при разработке на базе XDSP-680 высокочастотного спектро-анализатора сигналов реального времени с полосой до 10 МГц. В этом проекте М-модуль БПФ был соединен с М-модулем контроллера PCI в системе проектирования Foundation, полученная топология загружена в ПЛИС модуля XDSP. Дополнительно установлена дочерняя плата аналогового ввода (рис. 11) и на основе прилагающихся драйверов написана программа последующей обработки спектральной информации на персональном компьютере.

Рис. 11. Стыковка XDSP-680 с интерфейсом пользователя и PC

Стыковка XDSP-680 с интерфейсом пользователя и PCВ заключение отметим, что ПЛИС Xilinx благодаря своим богатым архитектурным особенностям и развитым средствам проектирования позволяют реализовывать мощные системы цифровой обработки сигналов с максимальной эффективностью по времени и качеству выполнения проекта и в конечном итоге по его стоимости.

Таблица 4. Характеристики М-модулей скользящего БПФ на ПЛИС Xilinx

| Число точек |

Тактовая частота, МГц |

Время преобразования, мкс |

Объем модуля, логических ячеек |

Требуемая ПЛИС |

| 128 |

150 |

1,0 |

7500 |

XCV400 |

| 256 |

150 |

2,0 |

9500 |

XCV400 |

| 512 |

150 |

4,0 |

13000 |

XCV600+внешн.ОЗУ |

| 1024 |

150 |

7,5 |

|

XCV600+внешн.ОЗУ |

Литература

- Xilinx Data Book, 1999, Xilinx, Inc.

- Программируемые логические ИМС на КМОП-структурах и их применение / П. П. Мальцев, Н. И. Гарбузов, А. П. Шарапов, Д. А. Кнышев. М.: Энергоатомиздат, 1998.

- Мистюков В. Г., Капитанов В. Д. Реализация высокопроизводительных сверхкомпактных КИХ-фильтров на ПЛИС Xilinx // Электроника и компоненты, 1998, № 4.

- Мистюков В. Г., Капитанов В. Д. Макромодули быстродействующих умножителей на ПЛИС Xilinx // Электроника и компоненты, 1998, № 3.

- Цифровая обработка сигналов: Справочник /Л. М. Гольденберг, Б. Д. Матюшкин, М. Н. Поляк. М.: Радио и связь, 1985.

- Капитанов В. Д., Володин П. В. Топологическая и временная оптимизация проектов на ПЛИС Xilinx // Компоненты и технологии, 1999, № 1, 2000, № 2.

- Цифровая обработка сигналов на ПЛИС Xilinx. Каталог продукции, 1999, Scan Engineering Telecom (код DSP-CAT-9906).

- Универсальная плата цифровой обработки сигналов XDSP-680. Техническое описание, 1998, Scan Engineering Telecom (код XDSP-680-DSH на http://www.xilinx.ru/ xdsp-680.htm).

- Универсальный модуль цифровой обработки сигналов SETCORE-1M. Техническое описание, 1999, Scan Engineering Telecom (код SETCORE-1M-DSH на http://www. xilinx.ru/setcore-1m.htm).

capt@scan.voronezh.su

www.xilinx.ru

|